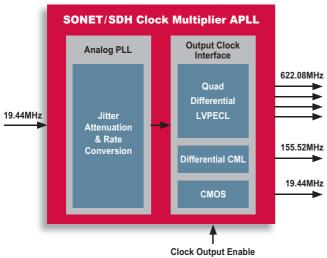

# **ZL30414 Simplified Block Diagram**

The ZL™ 30414 is the world's first SONET (synchronous optical network) and SDH (synchronous digital hierarchy) clock multiplier analog phase locked loop (APLL) to provide six output clocks from a single device with jitter performance that surpasses OC-192 and STM-64 system requirements. This unique level of integration and performance allows designers of SONET and SDH networking equipment to meet stringent timing requirements.

The ZL30414 APLL accepts a single reference input at 19.44 MHz and generates ultra-low jitter clock outputs in compliance with ITU-T and Telcordia jitter generation requirements for SONET/SDH equipment. With multiple clocks supporting CMOS, CML and LVPECL outputs, the ZL30414 eliminates external circuitry to save cost, board space and design resource requirements.

# **Applications**

→ SONET/SDH Line Cards

### At a Glance

- → Package: 64-pin TQFP

- Available now in production quantities

## **High Performance**

- Ultra-low jitter generation of 0.52ps rms (50kHz to 80MHz) surpasses world-wide system requirements.

- Meets Telcordia GR-253-CORE, from OC-1 to OC-192 rates.

- Meets ITU-T G.813 options 1 & 2, from STM-1 to STM-64 rates

## **Multiple Clock Outputs**

- Provides four differential LVPECL output clocks at 622.08MHz.

- → Differential CML output clock at 155.52MHz.

- → Single-ended CMOS clock at 19.44MHz.

# **Simplifies Design**

- ➤ Enables glueless interface to SONET/SDH devices such as framers, mappers and SERDES.

- Multiple LVPECL output clocks eliminate external circuitry for level conversion and fanout, saving board space, cost and design effort.

- → Simultaneously generates three different output frequencies from a standard CMOS reference input at 19.44MHz.

- Independent power down control of all output clocks optimizes power consumption.

### **Complementary Products**

- → MT9046 T1/E1 System Synchronizer Digital PLL

- → ZL30407 SONET/SDH Network Element Digital PLL

- → ZL30410 Multiservice Line Card PLL

# **Customer Support**

The ZL30414 is supported by a customer evaluation board (ZLE30414) and Zarlink's network of field application and design engineers.

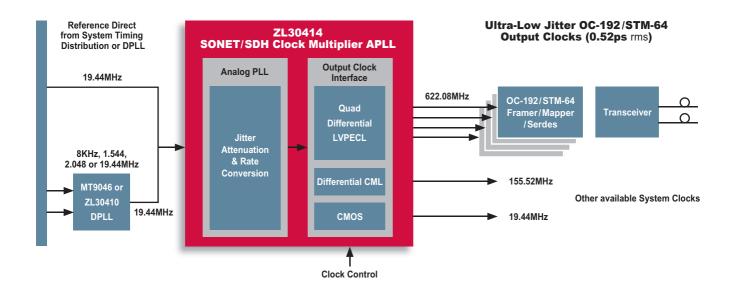

The following diagram represents an OC-192/STM-64 SONET/SDH Line Card application where the output clocks of the ZL30414 are used to drive framers, mappers and SERDES at various standard clock frequencies.

In this application the ZL30414 accepts a single 19.44MHz CMOS reference input directly from the timing card represented by the system timing distribution bus. When reference switching or advanced timing functionality are required on the line card, a digital PLL such as Zarlink's MT9046 or ZL30410 is used to provide the reference.

The ZL30414 filters jitter and multiplies the reference to common SONET/SDH frequencies available on six outputs. The device simultaneously generates three different clock frequencies.

Each output clock of the ZL30414 can be individually enabled or disabled, allowing designers to support the number of clocks required for specific system requirements. Un-needed clocks can be powered down optimizing power consumption.

The ability to support multiple, individually controlled output clocks substantially eases design compared to alternative solutions. The four LVLECL differential output clocks at 622.08 MHz interface directly to SONET/SDH devices eliminating external circuitry for level translation, fanout and enable/disable control. This reduces the bill of materials as well as the design effort required to consider and provision for the impact of this circuitry on clock signal and jitter performance.

The ZL30414 also reduces board space compared to VCO-based modules by up to 75 percent, and simplifies design versus discrete PLL implementations.

By simplifying the design of high-performance clocks, Zarlink enables OEMs to focus resources on the design of value-added features for the line card.

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively Zarlink) is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee expressed or implied is made regarding the capability, performance or suitability of any product or service.

ZARLINK, ZL, and the Zarlink logo are trademarks of Zarlink Semiconductor Inc. Copyright 2003, Zarlink Semiconductor Inc. All Rights Reserved.

Publication Number PP5854