# Prototyping for the RTSX-SU Enhanced Aerospace FPGA

#### **Table of Contents**

| Introduction                                                                |

|-----------------------------------------------------------------------------|

| Compatible Devices                                                          |

| Prototyping Flow                                                            |

| Prototyping Flow Description                                                |

| Prototyping Package Options                                                 |

|                                                                             |

| Prototyping with PQ208 for CQ208 and FG484 for CQ256 Packages and Sockets 5 |

| Prototyping with PQ208 for CQ208 and FG484 for CQ256 Packages and Sockets   |

| ,, o                                                                        |

| Special Considerations                                                      |

### Introduction

Microsemi<sup>®</sup>SoC Products Group provides radiation-tolerant FPGAs for space applications. However, since the enhanced environmental properties of radiation tolerant devices are not required during prototyping, inexpensive commercial equivalent devices can be substituted during this design phase. This application note describes the basic prototyping methodology for the space qualified RTSX-SU FPGA devices using the commercial equivalent SX-A FPGA devices. This application note includes the prototyping flow, prototyping package options, and other prototyping considerations.

## **Compatible Devices**

Since the RTSX-SU family of devices are 100% library compatible and density-matched with the SX-A family of devices, designers can first complete a design targeting the RTSX-SU, and then simply retarget the design to an equivalent SX-A device when prototyping. Refer to Table 1 for the correlation between the SX-A device and matching RTSX-SU device.

Table 1 • Equivalent RTSX-SU and SX-A Devices

| Device          | 32,000 Gates | 72,000 Gates |

|-----------------|--------------|--------------|

| RTSX-SU device  | RTSX32SU     | RTSX72SU     |

| SX-A equivalent | A54SX32A     | A54SX72A     |

## **Prototyping Flow**

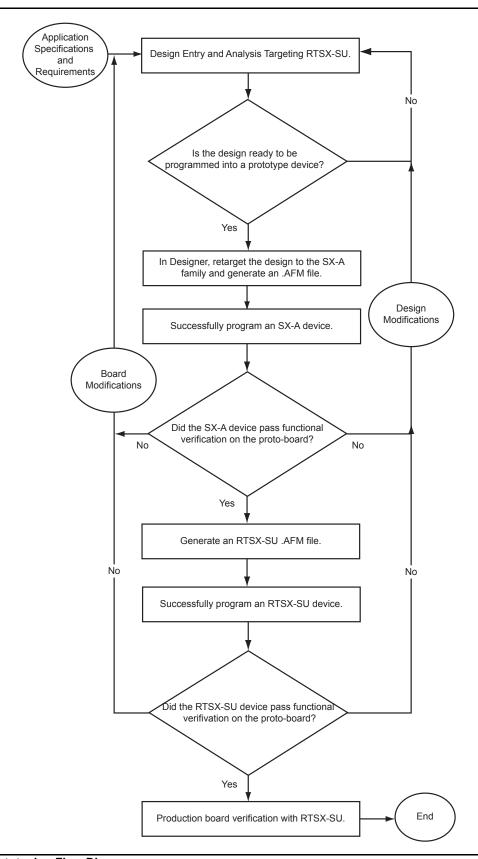

In order to produce designs that satisfy application specifications and requirements, designers may utilize various deign tools, techniques, and verification strategies. However, to increase efficiency when prototyping for the RTSX-SU, the recommended prototyping flow is illustrated in Figure 1 on page 3.

## **Prototyping Flow Description**

# Step 1: Complete All Application Specifications and Design Requirements

## Step 2: Target RTSX-SU in Designer and Complete Design Entry and Analysis

Implement the design targeting the RTSX-SU device in the SX-A family. This includes design capture (HDL or schematic), pre-synthesis simulation, synthesis, post-synthesis simulation, place-and-route, post-layout simulation, and static timing analysis. For designers using Libero™ Integrated Design Environment (IDE), refer to the latest version of Libero IDE online help or the user's guide for the *Libero IDE design flow*. Ensure to complete design-specific pin allocation, probe, and JTAG specification also. Note that for synthesis, Microsemi's Designer software uses RTSX-SU libraries for timing-driven synthesis for RTSX-SU. However, for simulation, SX-A libraries are used for both RTSX-SU and SX-A devices.

Then, during place-and-route and static timing analysis in Designer, you must target the RTSX-SU device to associate the correct package and timing information with the design.

Figure 1 • Prototyping Flow Diagram

#### Step 3: Retarget Design to the SX-A Device

Once the design meets functional and timing requirements, retarget the design to its commercial equivalent.

In Designer, retarget the design from RTSX-SU to SX-A by selecting the following option from the Designer software tools menu: Tools > Device Selection > SX-A. This methodology ensures that all of your design specifications and constraints are carried over to the prototype device few exceptions listed below.

When retargeting the SX-A device from the RTSX-SU device, consider the following:

- If the I/Os were previously configured as 5 V CMOS in the RTSX-SU design, they should be changed to 5 V TTL in the SX-A design. This is because the SX-A device family does not fully support 5 V CMOS I/Os. Therefore, during board-level verification, consider TLL and 5 V CMOS I/O specifications (that is VIH/VIL/VOH/VOL).

- 2. If the original targeted RTSX-SU device package is CQ256, select the FG484 for the SX-A device, as the SX-A device was not designed with a 256-pin plastic quad flat pack equivalent package. Note that repeating place-and-route is not required. See the "Prototyping Package Options" section on page 5 for details regarding the proper selection of prototyping device packages.

### Step 4: Program an SX-A Device

To program a device, you must first generate a\*.afm file, which is a design and package specific programming file. To generate a \*.afm file, click **FUSE** in the **Designer GUI** and select **.AFM** from the drop-down menu. Once the \*.afm file is generated the FUSE button turns green. The \*.afm file is the only file required for programming and contains two sections:

- Header section contains software and device information as well as the FUSECHECKSUM

- Programming section contains the encrypted programming information

Note: The \*.afm file programming content is different as it is appropriate for its targeted device family. Therefore, program the SX-A device only with the \*.afm file specifically generated for it. Likewise, program the RTSX-SU device only with the \*.afm file specifically generated for it. Mismatching or manually editing \*.afm files in any way is not supported

To program the SX-A or RTSX-SU device, you need the following materials:

- PC

- Silicon Sculptor III programmer

- · Silicon Sculptor III programming adaptor module (device package specific)

- Silicon Sculptor programming software (Windows or DOS version). Always use the latest version that is updated regularly on the Microsemi website.

- · Design specific \*.afm file

## Step 5: Perform Proto-Board-Level Verification with the SX-A Device

In addition to functional verification of the SX-A design, ensure to verify the power cycling sequence. A power cycling sequence of powering VCCA before VCCI is recommended for the RTSX-SU. See the RTSX-SU RadTolerant FPGAs for Space Applications datasheet for details. Also, in addition to JTAG testing, be sure to verify a workable procedure for the required grounding of the TRST pin. See the "TRST Pin" section on page 7 for more information.

### Step 6: Programming an RTSX-SU Device

Once the SX-A device successfully passes functional verification, generate a\*.afm file targeting the RTSX-SU device and program an RTSX-SU device.

## Step 7: Perform Proto-Board-Level Verification with the RTSX-SU Device

Repeat Step 5 using the RTSX-SU device.

#### **Step 8: Production Board Verification**

Finally, once the RTSX-SU device has been functionally verified on the proto-board, it is ready for production verification.

## **Prototyping Package Options**

In order to facilitate using a commercial device for prototyping, Microsemi has designed the RTSX-SU device in the CQ208 package to be pin compatible with the equivalent SX-A device in the CQ208 and PQ208 packages. This provides a simple method for customers to make a drop-in replacement from prototyping to production. Unfortunately, there is no equivalent PQ256 device package for the CQ256 package, so prototyping for this device package will have to be done using the FG484 package and a socket in order to match the CQ256 package footprint layout. Refer to the "Prototyping with PQ208 for CQ208 and FG484 for CQ256 Packages and Sockets" section for solder pad dimensions.

# Prototyping with PQ208 for CQ208 and FG484 for CQ256 Packages and Sockets

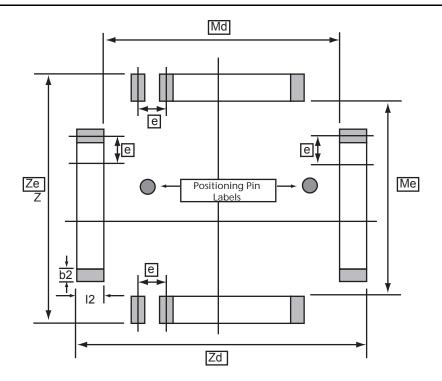

Figure 2 combined with Table 2 on page 6 shows the standard QFP solder pad layout for Microsemi quad flat packs and their associated dimensions.

Table 3 on page 6 contains board layout soldered pad dimensions to be employed if you are using a prototyping socket and either a CQ208, PQ208, or CQ256 package. These dimensions accept CQ208, PQ208, CQ256, and prototyping sockets.

Figure 2 • Solder Pad Layout

Table 2 • Combined PQ208/CQ208 and Prototype Socket / Combined CQ256 and CQ256-FG484 Adapter Socket

| Dimension <sup>1</sup> | PQ208/CQ208 <sup>2</sup> | CQ256 <sup>2</sup> /CQ256-FG484 Adapter Socket   |  |  |

|------------------------|--------------------------|--------------------------------------------------|--|--|

| Md                     | 28.2                     | 40.5                                             |  |  |

| me                     | 28.2                     | 40.5                                             |  |  |

| Zd                     | 35.1                     | 42.5                                             |  |  |

| Ze                     | 35.1                     | 42.5                                             |  |  |

| е                      | 0.5                      | 0.5                                              |  |  |

| b2                     | 0.3-0.4                  | 0.3-0.4                                          |  |  |

| 12                     | 1.6                      | 1.6                                              |  |  |

| Socket Part Number     | SY-PQG208 <sup>3</sup>   | SI-SX72-ACQ256SFG484 or SI-SX32-<br>ACQ256SFG484 |  |  |

<sup>1.</sup> Dimension = millimeters

Table 3 • Prototyping Grid

| Flight Part                   | RTSX32SU-<br>CQ84 | RTSX32SU-<br>CQ208       | RTSX32SU-<br>CQ256            | RTSX32SU-<br>CC256 | RTSX72SU-<br>CQ208       | RTSX72SU-<br>CQ256           | RTSX72SU-<br>CG624                                                           |

|-------------------------------|-------------------|--------------------------|-------------------------------|--------------------|--------------------------|------------------------------|------------------------------------------------------------------------------|

| Commercial<br>Equivalent Part | A54SX32A-<br>CQ84 | A54SX32A-<br>PQ208       | A54SX32A-<br>FG484            | Not<br>Available   | A54SX72A-<br>PQ208       | A54SX72A-<br>FG484           | A54SX72A-<br>FG484                                                           |

| Prototyping<br>Adaptor Board  |                   |                          | SI-SX32A-<br>ACQ256SF<br>G484 |                    |                          | SI-SX72-<br>ACQ256SF<br>G484 | SK-SX72-<br>CG624RTF<br>G484                                                 |

| Prototyping<br>Adaptor Socket |                   | SY-PQG208                |                               |                    | SY-PQG208                |                              |                                                                              |

| Pad Layout                    |                   | QFP solder<br>pad layout | QFP solder<br>pad layout      |                    | QFP solder<br>pad layout | QFP solder pad layout        | See the Microsemi CCGA to FBGA Adapter Socket Instructions application note. |

## **Special Considerations**

### **5 V CMOS Prototyping Concern**

Apart from the enhanced Single Event Upset (SEU) immunity, the RTSX-SU device has another capability, which the SX-A device lacks. The SX-A device has adjustable input trip points for TTL and PCI modes of operation. The RTSX-SU device has both of these as well as the 5 V CMOS input trip points. This feature allows the device to communicate more easily with certain CMOS devices, which are not designed for TTL noise margins. However, this poses a little difficulty when prototyping for a pure 5 V CMOS environment because the SX-A I/O thresholds are not fully CMOS compliant. For example,

<sup>2.</sup> Zd and Ze dimensions are based on trim and form data from Fancort Industries Inc. If you are using trim and form from another vendor, Zd and Ze could be different.

For the dimensions of the prototype socket, please refer to http://www,microsemi.com/soc/documents/sockets/20G.%20SY-PQG208.pdf

Microsemi's SX-A TTL outputs drive close to rail and can drive 5 V CMOS inputs, but SX-A TTL inputs have lower trip points and less noise margin than 5 V CMOS inputs.

#### **TRST Pin**

For RTSX-SU and SX-A, the TRST pin functions as a Dedicated Boundary-Scan Reset pin with an internal pull-up resistor that is permanently enabled on the TRST pin. For SX-A this pin can also be configured as a user I/O. However, this is not recommended for prototyping for RTSX-SU.

During prototyping, employ JTAG by pulling the TRST pin high. However, during flight, the RTSX-SU devices require the JTAG reset pin to be hardwired to ground. This prevents SEUs in the TAP controller from inadvertently placing the device into JTAG mode.

### Prototyping with RT\_PROTO Units

For the lower-cost prototyping and final design validation activities, Microsemi offers RTSX-SU, RTAX-S, RTAX-DSP, and RT ProASIC3 FPGAs in "RT-PROTO" form. RT-PROTO devices have the same footprint and timing characteristics as the flight units. They are intended for hardware timing verification only and they should not be used for space flight applications, which require the quality of space flight parts, such as qualification of space flight hardware. Refer to

www.microsemi.com/documents/RTPROTO\_Description.pdf for more information on prototyping for space flight design with Microsemi RT-PROTO FPGAs.

#### Conclusion

As it is essential to have a viable prototyping solution to streamline design and development of flight qualified designs, Microsemi produces commercial equivalent devices, prototyping sockets, and prototyping adaptor boards. By using the basic prototyping flow in this application note as a model and after first completing the design targeting the RTSX-SU device and then implementing the commercial equivalent SX-A as the prototyping device, it is apparent that prototyping for the RTSX-SU can become time and cost efficient.

#### **Related Documents**

#### **Datasheet**

RTSX-SU Radiation-Tolerant FPGAs (UMC)

### **Application Note**

Microsemi CCGA to FBGA Adapter Socket Instructions

#### **Miscellaneous**

Libero IDE Design Flow

## **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Revision*    | Changes                                                      | Page |

|--------------|--------------------------------------------------------------|------|

| Revision 2   | The Table 2 was updated (SAR 20911).                         | 6    |

| (April 2012) | The Table 3 was updated (SAR 20911).                         | 6    |

|              | The "Prototyping with RT_PROTO Units" was added (SAR 20911). | 7    |

Note: \*The revision number is located in the part number after the hyphen. The part number is displayed at the bottom of the last page of the document. The digits following the slash indicate the month and year of publication.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.